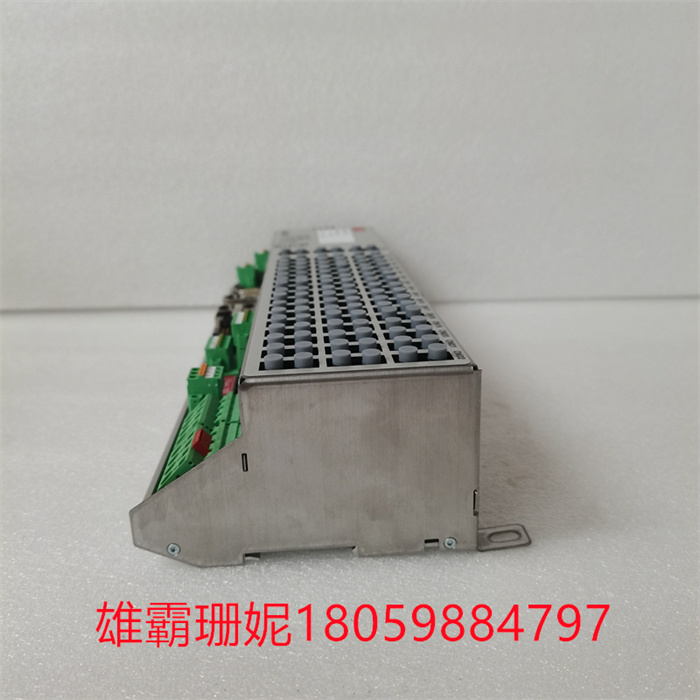

ABB GFD233A103 3BHE022294R0103 运动控制器

1、数据缓冲

由于I/O设备的速率较低而CPU和内存的速率却很高,故在控制器中必须设置一缓冲器。在输出时,用此缓冲器暂存由主机高速传来的数据,然后才以I/O设备所具有的速率将缓冲器中的数据传送给I/O设备;在输入时,缓冲器则用于暂存从I/O设备送来的数据,待接收到一批数据后,再将缓冲器中的数据高速地传送给主机。

2、差错控制

设备控制器还兼管对由I/O设备传送来的数据进行差错检测。若发现传送中出现了错误,通常是将差错检测码置位,并向CPU报告,于是CPU将本次传送来的数据作废,并重新进行一次传送。这样便可保证数据输入的正确性。

3、数据交换

这是指实现CPU与控制器之间、控制器与设备之间的数据交换。对于前者,是通过数据总线,由CPU并行地把数据写入控制器,或从控制器中并行地读出数据;对于后者,是设备将数据输入到控制器,或从控制器传送给设备。为此,在控制器中须设置数据寄存器。

4、状态说明

标识和报告设备的状态控制器应记下设备的状态供CPU了解。例如,仅当该设备处于发送就绪状态时,CPU才能启动控制器从设备中读出数据。为此,在控制器中应设置一状态寄存器,用其中的每一位来反映设备的某一种状态。当CPU将该寄存器的内容读入后,便可了解该设备的状态。

5、接收和识别命令

CPU可以向控制器发送多种不同的命令,设备控制器应能接收并识别这些命令。为此,在控制器中应具有相应的控制寄存器,用来存放接收的命令和参数,并对所接收的命令进行译码。例如,磁盘控制器可以接收CPU发来的Read、Write、Format等15条不同的命令,而且有些命令还带有参数;相应地,在磁盘控制器中有多个寄存器和命令译码器等。

6、地址识别

就像内存中的每一个单元都有一个地址一样,系统中的每一个设备也都有一个地址,而设备控制器又必须能够识别它所控制的每个设备的地址。此外,为使CPU能向(或从)寄存器中写入(或读出)数据,这些寄存器都应具有唯一的地址。

ABB GFD233A103 3BHE022294R0103 运动控制器

DMA控制器基本功能

(1)DMAC同外设之间有一对联络信号线——外设的DMA请求信号DREQ以及DMAC向外设发出的DMA响应信号DACK;

(2)DMAC在接收到DREQ后,同CPU之间也有一对联络信号线——DMAC向CPU发出总线请求信号(HOLD或BUSRQ),CPU在当前总线周期结束后向DMAC发出总线响应信号(HLDA或BUSAK),DMAC接管对总线的控制权,进入DMA操作方式;

(3)能发出地址信息,对存储器寻址,并修改地址指针,DMAC内部必须有能自动加1或减1的地址寄存器;

(4)能决定传送的字节数,并能判断DMA传送是否结束。DMA内部必须有能自动减1的字计数寄存器,计数结束产生终止计数信号;

(5)能发出DMA结束信号,释放总线,使CPU恢复总线控制权;

(6)能发出读、写控制信号,包括存储器访问信号和I/O访问信号。