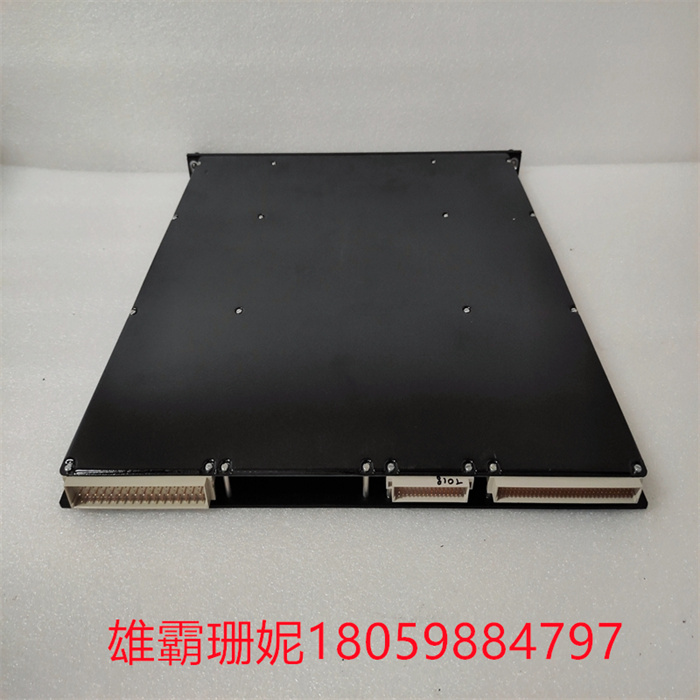

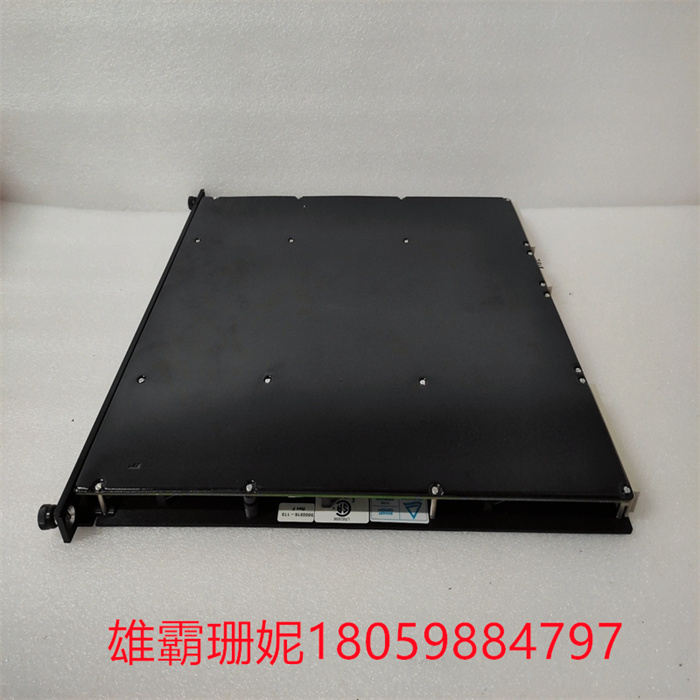

TRICONEX 3805E 模拟量输入模块

TRICONEX 3805E 模拟量输入模块

TRICONEX 3805E中的容错是通过三模几余(TMR)架构实现的。Tricon可在组件出现硬故障或内部或外部瞬时故障时提供无错误、不间断的控制Tricon采用完全三重架构设计,从输入模块到主处理器再到输出模块。每个I/O模块包含三个独立支路的电路。输入模块上的每个引脚读取过程数据,并将该信息传递给各自的主处理器。三个主处理器使用一种称为TriBus的专有高速总线系统相互通信。每扫描一次,三个主处理器通过TriBus与它们的两个邻居同步和通信。Tricon表决数字输入数据,比较输出数据并将模拟输入数据的副本发送到每个主处理器。主处理器执行用户编写的应用程序,并将应用程序生成的输出发送到输出模块。除了对输入数据进行投票TriBus还对输出数据进行投票。这在尽可能靠近场的输出模块上完成,以检测和补偿Tricon表决和驱动到场的最终输出之间的任何误差.

TRICONEX 3805E 模拟量输入模块

The fault tolerance in TRICONEX 3805E is realized by TMR architecture. Tricon can provide error-free and uninterrupted control in case of hard failure or internal or external transient failure of components. Tricon adopts a completely triple architecture design, from input module to main processor to output module. Each I/O module contains three independent branch circuits. Each pin on the input module reads the process data and transmits the information to its own main processor. The three main processors communicate with each other using a proprietary high-speed bus system called TriBus. Every scan, the three main processors synchronize and communicate with their two neighbors through TriBus. Tricon votes digital input data, compares output data and sends a copy of analog input data to each main processor. The main processor executes the application program written by the user and sends the output generated by the application program to the output module. In addition to voting on input data, TriBus also votes on output data. This is done on the output module as close to the field as possible to detect and compensate any error between Tricon voting and the final output driven to the field.

TRICONEX 3805E 模拟量输入模块